半導体の世界で「チップレット」という言葉を耳にする機会が増えてきました。AMDのRyzenプロセッサやAppleのMシリーズなど、最先端チップの多くがすでにこの技術を採用しています。

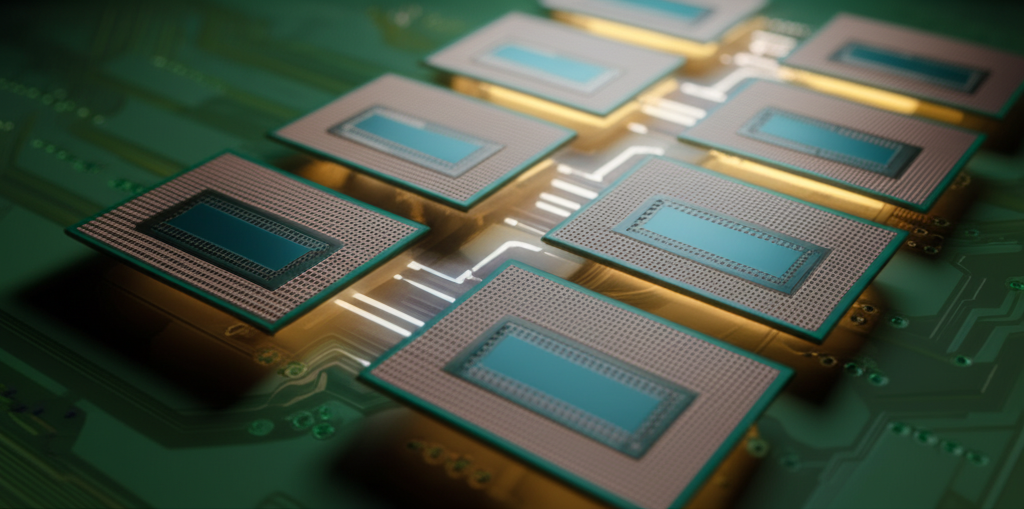

一言で言えば、チップレットとは「半導体のレゴブロック化」です。1つの巨大なチップを作るのではなく、機能ごとに分割した小さなチップ(チップレット)を組み合わせてプロセッサを構成する設計手法のことですね。

なぜチップレットが必要になったのか

背景にあるのは、ムーアの法則の鈍化です。半導体の微細化は3nmや2nmの世界に突入していますが、チップが大きくなるほど製造時の欠陥リスクが増加し、歩留まり(良品率)が下がります。

たとえば、100mm²のチップと400mm²のチップを同じウェハーから作る場合、大きいチップは1つの欠陥で丸ごと使えなくなるため、歩留まりが大幅に悪化します。結果としてコストが跳ね上がるわけです。

チップレットなら、小さなダイに分割することで歩留まりを改善できます。さらに、機能ごとに最適なプロセスノードを選べるのも大きなメリットです。CPUコアは最先端の3nmで、I/Oチップは安価な12nmで——といった「いいとこ取り」が可能になります。

チップレットの接続技術

チップレットを実現するうえで最も重要なのが、ダイ間の接続技術です。バラバラに作ったチップ同士を高速に通信させなければ、性能が出ません。

現在主流の接続方式には以下のようなものがあります。

- シリコンインターポーザ: チップレット間にシリコン基板を挟んで高密度配線する方式。TSMCのCoWoS(Chip-on-Wafer-on-Substrate)が代表的

- EMIB(Embedded Multi-die Interconnect Bridge): Intelが開発した、必要な箇所だけにシリコンブリッジを埋め込む効率的な手法

- UCIe(Universal Chiplet Interconnect Express): 2022年に策定されたチップレット間通信のオープン標準規格

特にUCIeは業界標準として注目されています。Intel、AMD、Arm、TSMC、Samsung、Qualcommなどが参加しており、異なるメーカーのチップレットを組み合わせる「ミックス&マッチ」の世界が現実味を帯びてきました。

AI時代にチップレットが重要な理由

チップレット技術がいま特に注目される理由は、AI需要の爆発的な増加にあります。

AIアクセラレータ(GPU/TPU)はどんどん巨大化しており、NVIDIAのB200は814mm²というモノリシックチップの物理的限界に近いサイズです。これ以上の性能向上には、チップレットによるスケールアウトが不可欠になっています。

実際、AMDのInstinct MI300Xは13個のチップレットを組み合わせた構成で、LLMの推論コスト削減に貢献するHBM(High Bandwidth Memory)チップレットを高密度に実装しています。

コスト面のメリット

チップレットのコストメリットは想像以上に大きいようです。半導体業界のアナリストによると、チップレット設計への移行で製造コストを30〜50%削減できるケースもあるとのこと。

また、一度設計したチップレットを複数の製品で再利用できる点も見逃せません。サーバー向けとデスクトップ向けでCPUコアのチップレットを共通化し、I/Oやメモリコントローラだけ変えるといった柔軟な製品展開が可能になります。AMDがEPYCとRyzenでこの戦略を成功させているのは有名な話です。

課題と今後の展望

もちろん課題もあります。チップレット間の通信レイテンシ、熱管理の複雑化、そしてテストとデバッグの難しさなどが挙げられます。特に異なるメーカーのチップレットを組み合わせる場合、互換性の検証は容易ではありません。

それでも、UCIe 2.0の策定や先進パッケージング技術の進化により、2026年現在、チップレットは「未来の技術」から「現在進行形の標準設計手法」へと移行しつつあります。

Qwen3.5のようなマルチモーダルAIモデルの実行に必要な計算能力を効率的に提供するうえでも、チップレット技術の進化は欠かせないピースだと感じます。

まとめ

チップレット技術は、半導体業界が直面する物理的・経済的な壁を乗り越えるための現実的な解決策です。「大きなチップを1つ作る」から「小さなチップを組み合わせる」へのパラダイムシフトは、ソフトウェア開発におけるマイクロサービスへの移行と似た構造的な変化だと言えるかもしれません。

AI需要の拡大とともに、チップレットの重要性は今後さらに増していくことが予想されます。半導体に興味がある方は、UCIeの動向を追っておくと面白いのではないでしょうか。